[지디넷코리아]

“이제는 칩 하나가 얼마나 잘 돌아가는지를 넘어, 실제 보드와 시스템 위에서 작동하는 서비스를 증명해야 하는 단계입니다.”

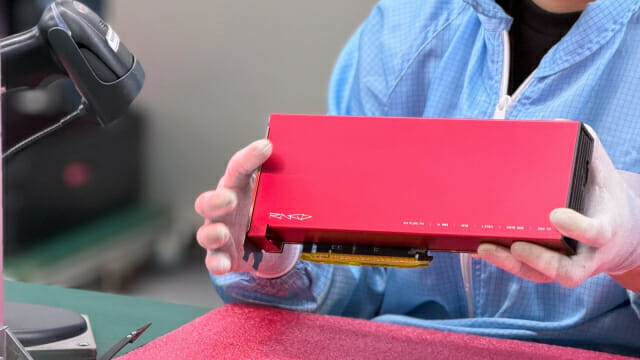

김지훈 한양대학교 융합전자공학부 교수는 최근 본지와의 인터뷰에서 국내 AI 반도체 팹리스들의 현주소를 이같이 진단했다. 하드웨어 설계 역량은 이미 글로벌 톱티어 수준에 도달했으나, 실제 시장에서 엔비디아의 대안으로 자리 잡기 위해서는 시스템 단위에서 안정성과 소프트웨어 포팅(Porting) 편의성을 입증하는 ‘실무적 검증’이 최우선 과제라는 설명이다.

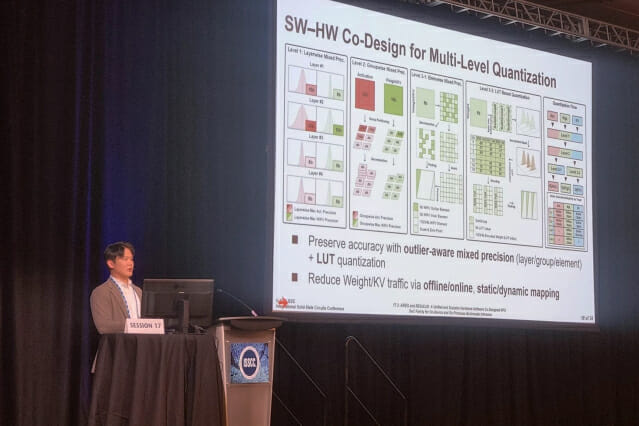

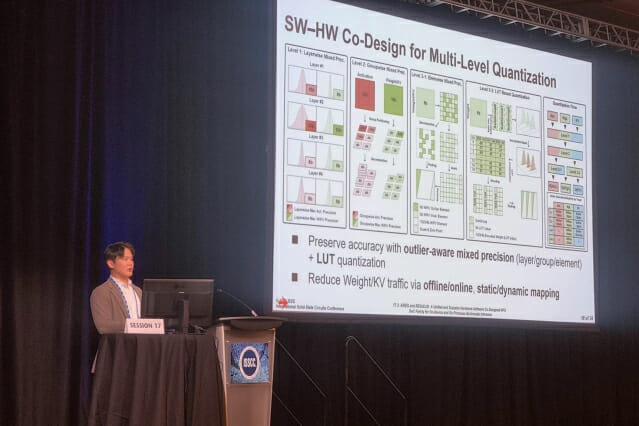

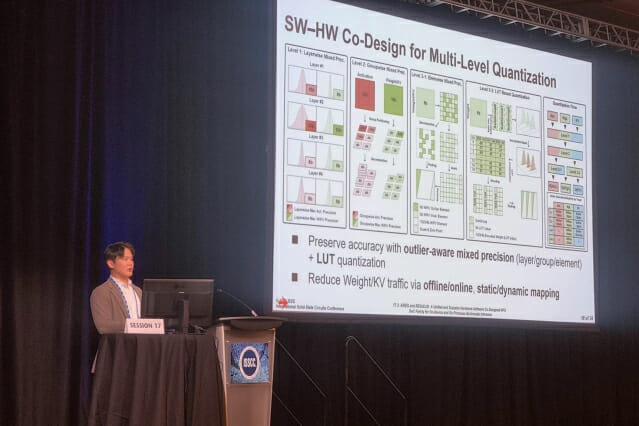

올해 국제고체회로학회(ISSCC)에서 리벨리온, 모빌린트 등 국내 AI 반도체 기업들이 보여준 성과는 단순한 학술적 발표에 머물지 않았다.

ISSCC는 국제 반도체 올림픽 IEEE(전기전자공학자협회)가 주관하는 세계 최대 규모 반도체 IC(집적회로) 설계 학술대회로, 반도체 올림픽으로도 불린다. 김 교수는 ISSCC DAS(Digital Architectures & systems)분과 TPC(기술 프로그램 위원회)를 올해 2월까지 담당했다. TPC의 역할은 논문을 심사 및 선정하고, 세션을 구성한다.

김 교수는 현장 분위기에 대해 “과거가 칩 하나가 얼마나 잘 돌아가는지를 증명하는 시기였다면, 이제는 여러 개의 칩을 묶어 보드와 시스템 단위로 확장(Scale-out)했을 때 실제 서비스가 원활하게 배포될 수 있는지를 보여주는 단계로 진입했다”고 평했다.

특히 생성형 AI 시장이 급팽창하며 LLM(거대언어모델) 가속을 위한 시스템 단위의 성능 구현이 팹리스들의 핵심 과제로 부상했다.

김 교수는 “현장에서 확인된 국내 기업들의 기술적 성취는 HBM3E와 같은 최신 고대역폭 메모리 적용과 선단 공정 인터페이스 도입 측면에서 글로벌 선도 기업과 어깨를 나란히 했다”며 “다만 수요 기업 입장에서는 하드웨어 스펙보다 기존 GPU 환경에서 개발된 모델을 얼마나 적은 비용으로 NPU에 이식할 수 있는지가 관건”이라고 짚었다.

이어 “사용자의 전환 비용을 낮추고 전체 인프라 운영 비용(TCO) 절감 효과를 수치로 입증해야만 엔비디아의 독주 체제 속에서 실질적인 1차 선택지가 될 수 있다”며, 단순히 칩의 연산 속도가 빠른 것을 넘어 개발자가 엔비디아의 ‘쿠다(CUDA)’를 사용할 때와 유사한 편의성을 체감할 수 있는 소프트웨어 스택의 성숙도가 시장 안착의 분수령이 될 것이라고 분석했다.

정부가 추진하는 ‘K-엔비디아 프로젝트’를 통한 5대 NPU 기업 집중 지원은 초기 시장 형성을 위해 불가피한 측면이 있다. 하지만 김 교수는 특정 선도 기업에만 자금이 쏠리는 현상이 장기적으로 국내 시스템 반도체 생태계의 허리를 약화할 수 있다는 우려를 숨기지 않았다. AI 인프라는 연산을 담당하는 NPU 하나로 완성되지 않기 때문이다.

실제로 메모리 확장을 위한 CXL(파네시아), 고속 검색 및 저장 최적화를 위한 VDPU(디노티시아), 데이터 처리를 돕는 DPU(망고부스트) 등 다양한 분야의 플레이어들이 유기적으로 결합해야 강력한 시스템 경쟁력이 생긴다.

김 교수는 “삼성 파운드리 생태계의 핵심인 디자인솔루션파트너(DSP)들의 역량 강화를 포함해 특수 목적 칩을 설계하는 중소 팹리스들까지 두루 육성하는 포괄적 전략이 수반되어야 한다”고 조언했다.

그러면서 “소수 기업이 상장에 성공한 뒤 그 성과가 생태계 전반으로 낙수 효과를 일으킬 수 있도록, 설계 IP부터 패키징에 이르는 전후방 산업의 자생력을 동시에 키워야 한다”고 거듭 강조했다.

지속 가능한 성장을 위한 인적·물적 토대는 오히려 약화하고 있다고 진단했다. 김 교수가 가장 우려하는 대목은 반도체설계교육센터(IDEC)의 예산 삭감 문제다.

그는 “IDEC은 전국의 대학원생과 연구자들에게 값비싼 설계 툴(EDA)을 지원하고 시제품 제작(MPW) 기회를 제공하는 국내 팹리스 산업의 젖줄”이라며 “이러한 기초 인프라 예산의 위축은 미래 설계 인력들의 실무 경험 축소를 야기하고, 결국 중장기적인 산업 경쟁력 저하로 이어질 수밖에 없다”고 지적했다.

시제품 하나를 만드는 데 수억 원이 드는 환경에서 대학의 설계 경험이 단절되면 기업이 필요로 하는 실무형 인재 확보는 더욱 어려워질 수밖에 없다는 의견이다.

인재 양성 정책의 단절성도 시급한 해결 과제로 꼽혔다. 김 교수는 “AI 반도체 대학원 등 주요 교육 사업이 5년 단위의 단기 기금 사업으로 운영되다 보니 연구의 연속성과 전문성을 담보하기 어렵다”고 토로했다. 글로벌 빅테크 기업들이 국내 우수 인력을 파격적인 조건으로 흡수하고 있는 상황에서, 국내 팹리스 산업의 허리를 담당할 실무 인재를 꾸준히 배출하려면 기초 교육 인프라에 대한 흔들림 없는 지원 체계가 선행되어야 한다는 것이다.

김 교수는 인터뷰를 마치며 “칩 설계 역량은 이미 궤도에 올랐지만, 이를 시스템으로 구현하고 운영할 인재와 인프라가 뒷받침되지 않으면 K-AI칩의 기세는 일회성 돌풍에 그칠 수 있다”며 정책의 지속성과 생태계 전반에 대한 관심을 거듭 당부했다.